(ご注意)今回は前編の続きです。まず前編を読まれることを推奨します。

スーパービアがブロックする配線本数を減らしたときの問題

前編では、「スーパービア(supervia)」が抱える本質的な課題を説明した。中間配線層のレイアウトがスーパービアによって阻害されるという問題である。前編では1本のスーパービアがブロックする配線数(トラック数)を増やしたときに生じる問題を具体的に説明した。配線混雑度の上昇と、レイアウト設計ツールが検出するルール違反(DRC違反)の増大である。

後編では、1本のスーパービアがブロックするトラック数を減らしたときに生じる問題と、解決策を述べる。想定しているのは、垂直(縦)方向に平行直線状の第1層金属配線(M1)と第3層金属配線(M3)をレイアウトし、水平(横)方向に平行直線状の第2層金属配線(M2)をレイアウトする論理回路セル(スタンダードセル)である。トラックの高さは5トラック(5T)。ナノシート構造のトランジスタと埋め込み電源(BPR)を採用している。スーパービアはM1とM3をダイレクトに接続する。すなわちスーパービアによってM2がブロックされる。

3nm世代を想定した第1層(M1)から第3層(M3)までの多層配線構造とリソグラフィ技術(再掲)。配線層とビア電極の金属はルテニウム(Ru)。左図は第2層(M2)を横切る方向の断面構造。右図はM1およびM3を横切る方向の断面構造[クリックで拡大] 出所:imec(IEDM 2020の発表論文「Supervia Process Integration and Reliability Compared to Stacked Vias Using Barrierless Ruthenium」(論文番号20.5))

3nm世代を想定した第1層(M1)から第3層(M3)までの多層配線構造とリソグラフィ技術(再掲)。配線層とビア電極の金属はルテニウム(Ru)。左図は第2層(M2)を横切る方向の断面構造。右図はM1およびM3を横切る方向の断面構造[クリックで拡大] 出所:imec(IEDM 2020の発表論文「Supervia Process Integration and Reliability Compared to Stacked Vias Using Barrierless Ruthenium」(論文番号20.5))配線レイアウトの自由度をなるべく高くするためには、ブロックするトラック数は少ないことが望ましい。1本のスーパービアがブロックするM2のトラック数が最も少ないのは、1トラック(1本)である。そこでブロックするトラック数を、1トラックから順番に2トラック、3トラックと増やしていく。これらの条件で第1層(M1)から第3層(M3)までの多層配線構造を試作し、スーパービアの特性を測定した。

ブロックするトラック数を変えて試作した多層配線構造のレイアウトと断面の電子顕微鏡観察像。左端はブロックしたM2のトラック数。上から3トラック、2トラック、1トラックである。中央と右端は配線構造の断面観察像。それぞれ、左端のブロック数に対応している。中央はM2に平行で、M3とM1を横切る方向の断面。右端はM3とM1に平行で、M2を横切る方向の断面。断面画像中の黄色い数値はスーパービア各部の寸法[クリックで拡大] 出所:imec(IEDM 2020の発表論文「Supervia Process Integration and Reliability Compared to Stacked Vias Using Barrierless Ruthenium」(論文番号20.5))

ブロックするトラック数を変えて試作した多層配線構造のレイアウトと断面の電子顕微鏡観察像。左端はブロックしたM2のトラック数。上から3トラック、2トラック、1トラックである。中央と右端は配線構造の断面観察像。それぞれ、左端のブロック数に対応している。中央はM2に平行で、M3とM1を横切る方向の断面。右端はM3とM1に平行で、M2を横切る方向の断面。断面画像中の黄色い数値はスーパービア各部の寸法[クリックで拡大] 出所:imec(IEDM 2020の発表論文「Supervia Process Integration and Reliability Compared to Stacked Vias Using Barrierless Ruthenium」(論文番号20.5))絶縁とレイアウトを両立させるブロック数は「3トラック」

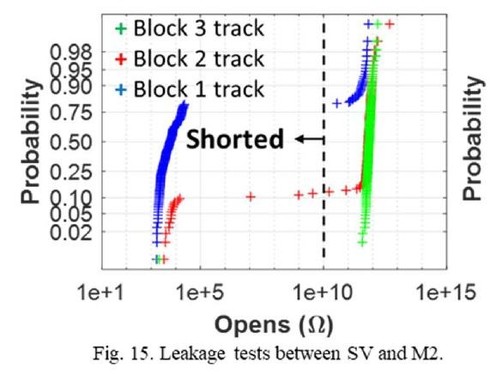

特に重視したのは、スーパービアとM2の絶縁抵抗である。絶縁抵抗(リーク電流)を測定したところ、ブロックするM2が1トラックの場合は75%のスーパービアが短絡不良を生じた。ブロックするM2が2トラックでも、10%のスーパービアが短絡不良を起こしている。3トラックになると、ようやく短絡不良が目立たなくなる。

スーパービアとM2の絶縁抵抗。縦軸は累積確率。横軸は電気抵抗値[クリックで拡大] 出所:imec(IEDM 2020の発表論文「Supervia Process Integration and Reliability Compared to Stacked Vias Using Barrierless Ruthenium」(論文番号20.5))

スーパービアとM2の絶縁抵抗。縦軸は累積確率。横軸は電気抵抗値[クリックで拡大] 出所:imec(IEDM 2020の発表論文「Supervia Process Integration and Reliability Compared to Stacked Vias Using Barrierless Ruthenium」(論文番号20.5))この結果から、少なくとも3トラックのM2をブロックすべきであることが分かる。また前編で述べたように、4トラックあるいは5トラックのブロックは配線レイアウトを阻害することが明らかになっている。取りあえずは3トラックが最適なように見える。

そこで3トラックのM2をブロックしたスーパービアの電気抵抗(ビア抵抗)を、アスペクト比が3のスタックビアと比較したところ、ビア抵抗の中央値はスーパービアがスタックビアの2.4分の1と大幅に低かった。スーパービアは、ビア抵抗の低減技術として十分に期待できる。

異なるビアの電気抵抗値を4端子法(ケルビン接続)によって測定した結果。3トラックのM2をブロックしたスーパービア(SV)の抵抗値は、スタックビア(アスペクト比3)の2.4分の1と低い[クリックで拡大] 出所:imec(IEDM 2020の発表論文「Supervia Process Integration and Reliability Compared to Stacked Vias Using Barrierless Ruthenium」(論文番号20.5))

異なるビアの電気抵抗値を4端子法(ケルビン接続)によって測定した結果。3トラックのM2をブロックしたスーパービア(SV)の抵抗値は、スタックビア(アスペクト比3)の2.4分の1と低い[クリックで拡大] 出所:imec(IEDM 2020の発表論文「Supervia Process Integration and Reliability Compared to Stacked Vias Using Barrierless Ruthenium」(論文番号20.5))(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

からの記事と詳細 ( 2層上下の配線層をダイレクトに接続する「スーパービア」の課題(後編) - EE Times Japan )

https://ift.tt/3zUVSXf

No comments:

Post a Comment